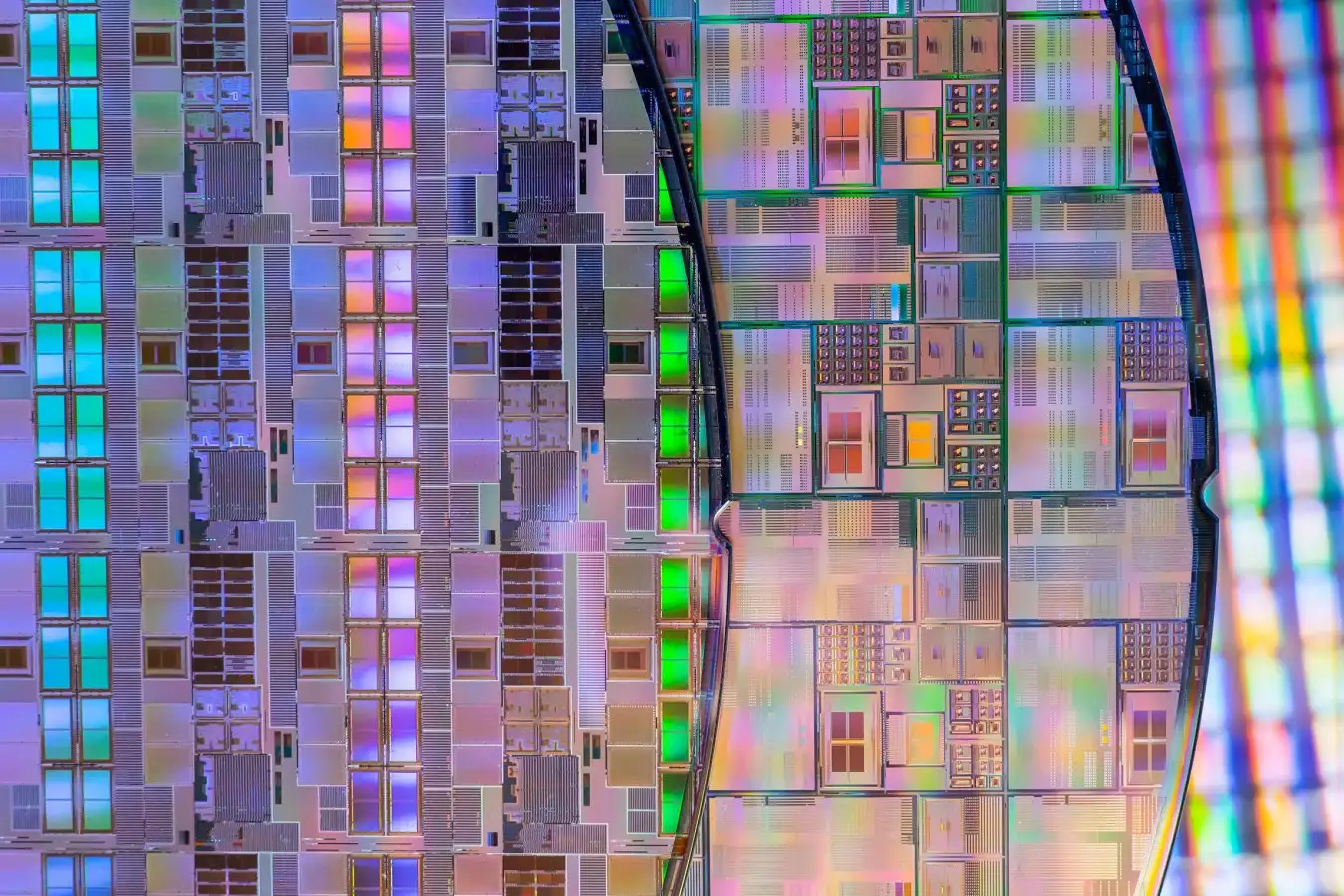

Current silicon chips are highly compact, but using ultrathin 2D materials could enhance their density even further.

Wu Kailiang/Alamy

A memory chip with a thickness of just 10 atoms could revolutionize the storage capacity of electronic gadgets like smartphones.

Despite decades of scaling down, modern computer chips often have very few components yet integrate tens of billions of transistors into an area comparable to a fingernail. Although the size of silicon components has significantly decreased, the thickness of the silicon wafers remains considerable, imposing limitations on increasing a chip’s complexity through stacking layers.

Researchers have been exploring the potential of thinner chips made from 2D materials like graphene. Graphene consists of a single layer of carbon atoms and represents the thinnest known material. However, until recently, only basic chip designs could be implemented with these materials, complicating their connection to traditional processors and integration into electrical devices.

Recently, Liu Chunsen and his team from Fudan University in Shanghai successfully integrated a 2D chip only 10 atoms thick with a CMOS chip currently utilized in computers. The manufacturing method for these chips yields a rough surface, making it challenging to layer a 2D sheet on top. The researchers addressed this issue by placing a glass layer between the 2D and CMOS chips, although this step is not yet part of the industrial process and requires further development for mass production.

The prototype memory module the team created achieved over 93% accuracy during testing. While this falls short of the reliability needed for consumer-grade devices, it serves as an encouraging proof of concept.

“This technology holds significant promise, but there’s still a considerable journey ahead before it can be commercialized,” says Steve Furber from the University of Manchester, UK.

Kai Shu, a researcher at King’s College London, mentions that further reducing current chip designs without utilizing 2D materials poses challenges due to signal leakage associated with traditional components made at very narrow widths. Thinner layers might mitigate this issue. Consequently, achieving greater thinness may facilitate additional reductions in width.

“Silicon is encountering hurdles,” said Xu. “2D materials might provide solutions. With their minimal thickness, gate control becomes more uniform and comprehensive, resulting in reduced leakage.”

topic:

Source: www.newscientist.com